FPGA必学!同步异步FIFO全面解析!

在数字电路和FPGA(现场可编程门阵列)设计中,FIFO(先进先出)缓存器扮演着至关重要的角色。无论是作为数据缓冲还是用于时钟域的隔离,FIFO都能提供高效的解决方案。本文将带你深入了解同步FIFO和异步FIFO的工作原理、应用场景以及设计要点,让你在FPGA的学习之路上更进一步。

FIFO,即先进先出(First In First Out)缓存器,是一种特殊类型的存储器件,主要用于数据缓冲和流控制。与普通存储器不同,FIFO没有外部读写地址线,只能按照数据的写入顺序进行读取。这种特性使得FIFO在数据处理中非常高效,尤其适用于需要连续、高速数据传输的场合。

在数据传输过程中,由于数据源和目的地的速率不匹配,往往会出现数据写入过快或间隔时间过长的情况。这时,通过设置一定深度的FIFO作为缓冲区,可以有效避免数据丢失,保证数据的完整性和连续性。FIFO还可以平滑处理流程,减少数据处理延迟。

在数字电路设计中,不同模块或设备之间可能存在时钟差异。当数据需要在不同时钟域之间传输时,就需要使用FIFO进行隔离。异步FIFO可以很好地解决跨时钟域数据传输带来的问题,避免亚稳态和数据损坏的风险。例如,在ADC(模数转换器)与DSP(数字信号处理器)之间的数据传输中,ADC的采样速率可能与DSP的处理速率不匹配。这时,可以通过设置异步FIFO来缓存ADC的数据,以供DSP按照自身速率进行读取。

根据读写时钟的不同,FIFO可以分为同步FIFO和异步FIFO两类。

同步FIFO的读写时钟是同一个时钟源。这种FIFO设计简单,易于实现。但由于读写操作都在同一个时钟域内进行,因此无法直接用于跨时钟域的数据传输。

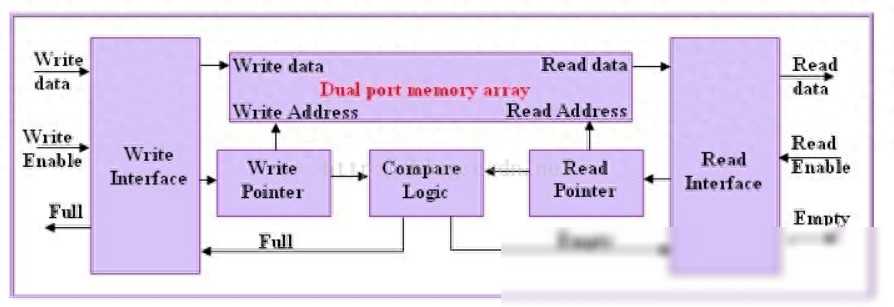

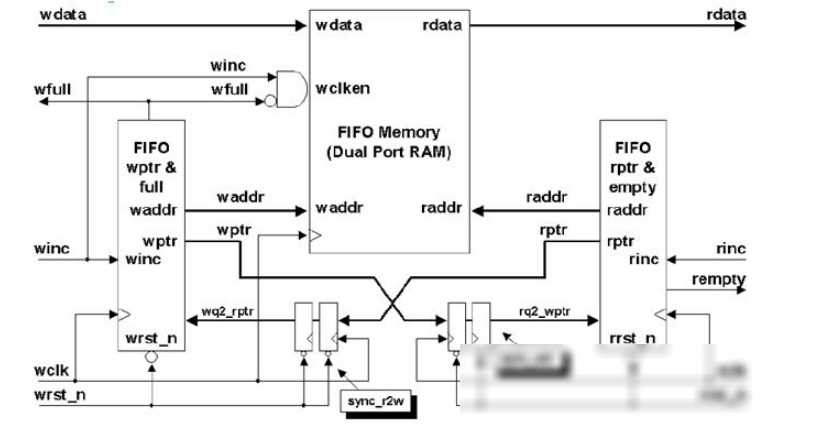

异步FIFO的读写时钟是不同的时钟源。这种FIFO可以实现跨时钟域的数据传输,解决了不同时钟域之间的数据传输问题。但是,由于读写操作发生在不同时钟域内,因此设计时需要特别注意跨时钟域问题的处理。

FIFO的宽度指的是一次读写操作的数据位数。这个参数决定了FIFO能够处理的数据类型和数据量。例如,一个8位宽的FIFO可以一次读写一个字节的数据;而一个32位宽的FIFO则可以一次读写一个整型数据。

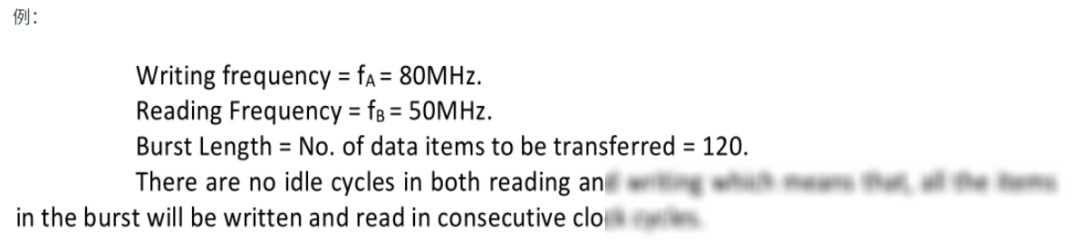

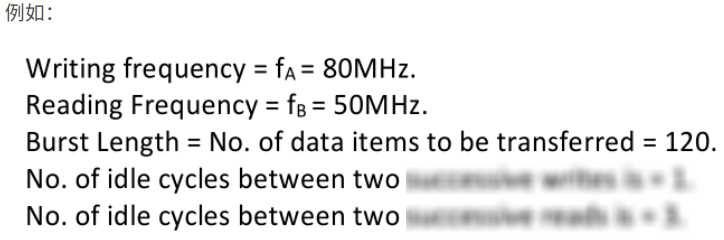

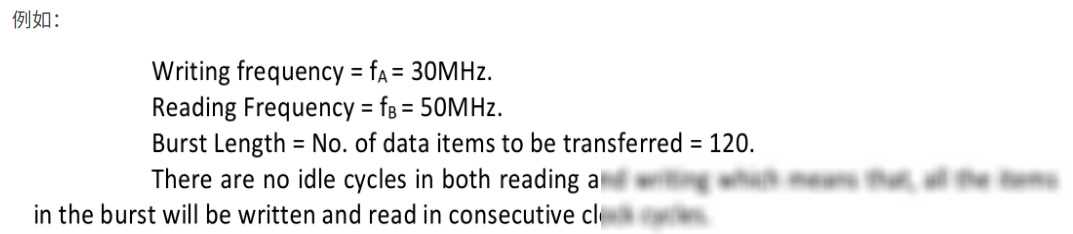

FIFO的深度指的是FIFO能够存储的数据单元数(如果宽度为N位,则每个数据单元为N位)。这个参数决定了FIFO的缓冲能力。例如,一个深度为16的FIFO可以存储16个数据单元;而一个深度为256的FIFO则可以存储更多的数据单元,以应对更大的数据缓冲需求。

满标志和空标志是FIFO的两个重要状态标志。当FIFO中的数据量达到最大值时,满标志会被置位;当FIFO中的数据被全部读取后,空标志会被置位。这两个标志可以帮助我们及时了解FIFO的状态,以便进行相应的数据处理和控制。

在FIFO设计中,空满标志的生成是关键之一。为了保证数据的正确性和稳定性,我们需要采用可靠的方法来检测FIFO的空满状态。一种常用的方法是在读写指针中添加一个额外的位(如M**),通过比较读写指针的该位来判断FIFO是否处于空或满状态。

异步FIFO的设计需要考虑跨时钟域问题。为了避免亚稳态和数据损坏的风险,我们需要采用一些特殊的措施来同步读写指针和状态标志。例如,可以使用格雷码(Gray Code)来编码读写指针,以减少在跨时钟域同步时可能出现的错误。此外,我们还需要在设计中加入适当的延时和滤波电路来确保数据的稳定性和可靠性。

在FIFO设计中,性能优化也是一个重要的考虑因素。为了提高FIFO的读写速度和吞吐量,我们可以采用一些优化策略。例如,可以增加FIFO的并行读写能力;采用更高效的算法来管理读写指针和状态标志;以及利用FPGA的并行处理能力来加速数据处理等。

通过本文的介绍,相信你已经对同步FIFO和异步FIFO有了更深入的了解。在实际应用中,我们可以根据具体的需求和场景选择合适的FIFO类型和设计方法。我们也需要不断学习和探索新的技术和方法,以应对日益复杂和多变的设计需求。让我们携手共进,在FPGA的学习之路上不断前行!